Description

This project was for one of the labs in EECE2160 embedded design. The goal of this lab was the create an algorithmic-logic unit (ALU) on an Intel DE1-SoC FPGA. The ALU operated on 8-bit unsigned integers and could do basic math (add, subtract, multiply, divide). The results of the math would then be displayed on the 7-segment displays on the board. Intel Quartus was used to program the board. Before any math, the 7-segment displays had to be programmed to display integers. After that, mathematical functions were added using the IP catalog library on Intel Quartus. Switches and a multiplexer were programmed to correspond to numbers and functions. Once programmed, various mathematical expressions were tested. Any lab reports regarding this lab are avaliable upon request.

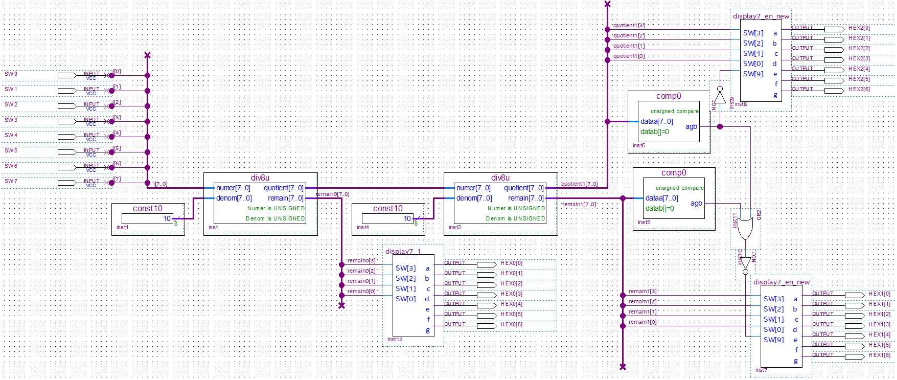

Circuit for 8-bit Display

Photos of Display Functioning

8-bit display with 255 as input

8-bit display with 99 as input

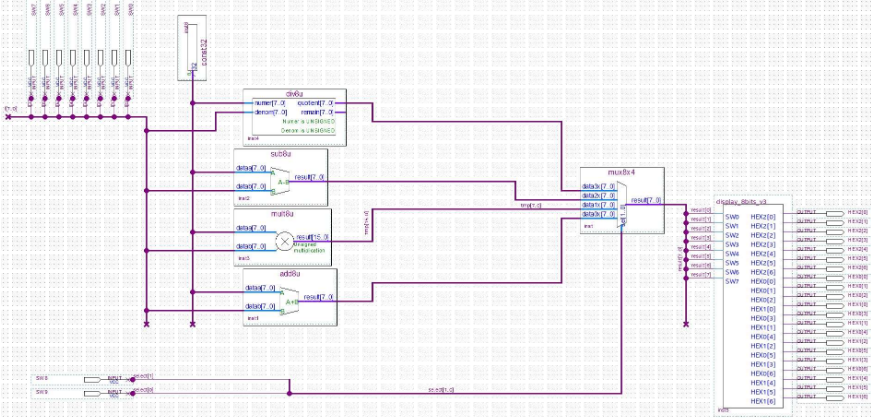

Circuit for 8-bit ALU

Photos of ALU functioning

Addition using ALU (32+38)

Subtraction using ALU (32-13)

Multiplication using ALU (32*5)

Division using ALU (32/4)